Guidance for Aging Management of Instrumentation and Control (I&C) Circuit Cards and Components Based on Électricité de France (EDF) Experience

## Guidance for Aging Management of Instrumentation and Control (I&C) Circuit Cards and Components Based on Électricité de France (EDF) Experience

1022246

Final Report, November 2010

EPRI Project Manager J. Naser

#### DISCLAIMER OF WARRANTIES AND LIMITATION OF LIABILITIES

THIS DOCUMENT WAS PREPARED BY THE ORGANIZATION(S) NAMED BELOW AS AN ACCOUNT OF WORK SPONSORED OR COSPONSORED BY THE ELECTRIC POWER RESEARCH INSTITUTE, INC. (EPRI). NEITHER EPRI, ANY MEMBER OF EPRI, ANY COSPONSOR, THE ORGANIZATION(S) BELOW, NOR ANY PERSON ACTING ON BEHALF OF ANY OF THEM:

- (A) MAKES ANY WARRANTY OR REPRESENTATION WHATSOEVER, EXPRESS OR IMPLIED, (I) WITH RESPECT TO THE USE OF ANY INFORMATION, APPARATUS, METHOD, PROCESS, OR SIMILAR ITEM DISCLOSED IN THIS DOCUMENT, INCLUDING MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, OR (II) THAT SUCH USE DOES NOT INFRINGE ON OR INTERFERE WITH PRIVATELY OWNED RIGHTS, INCLUDING ANY PARTY'S INTELLECTUAL PROPERTY, OR (III) THAT THIS DOCUMENT IS SUITABLE TO ANY PARTICULAR USER'S CIRCUMSTANCE; OR

- (B) ASSUMES RESPONSIBILITY FOR ANY DAMAGES OR OTHER LIABILITY WHATSOEVER (INCLUDING ANY CONSEQUENTIAL DAMAGES, EVEN IF EPRI OR ANY EPRI REPRESENTATIVE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES) RESULTING FROM YOUR SELECTION OR USE OF THIS DOCUMENT OR ANY INFORMATION, APPARATUS, METHOD, PROCESS, OR SIMILAR ITEM DISCLOSED IN THIS DOCUMENT.

THE FOLLOWING ORGANIZATION(S), UNDER CONTRACT TO EPRI, PREPARED THIS REPORT:

#### **EDF R&D**

THE TECHNICAL CONTENTS OF THIS DOCUMENT WERE <u>NOT</u> PREPARED IN ACCORDANCE WITH THE EPRI NUCLEAR QUALITY ASSURANCE PROGRAM MANUAL THAT FULFILLS THE REQUIREMENTS OF 10 CFR 50, APPENDIX B AND 10 CFR PART 21, ANSI N45.2-1977 AND/OR THE INTENT OF ISO-9001 (1994). USE OF THE CONTENTS OF THIS DOCUMENT IN NUCLEAR SAFETY OR NUCLEAR QUALITY APPLICATIONS REQUIRES ADDITIONAL ACTIONS BY USER PURSUANT TO THEIR INTERNAL PROCEDURES.

#### **NOTE**

For further information about EPRI, call the EPRI Customer Assistance Center at 800.313.3774 or e-mail askepri@epri.com.

Electric Power Research Institute, EPRI, and TOGETHER...SHAPING THE FUTURE OF ELECTRICITY are registered service marks of the Electric Power Research Institute, Inc.

COPYRIGHT © 2010 ELECTRIC POWER RESEARCH INSTITUTE, INC. ALL RIGHTS RESERVED.

Copyright © 2010 Electric Power Research Institute, Inc. All rights reserved. Disclaimer AutoText for EPRI.

#### **ACKNOWLEDGMENTS**

The following organization(s), under contract to the Electric Power Research Institute (EPRI), prepared this report:

EDF R&D – Electrical Material Laboratory Avenue des Renardières - Ecuelles 77818 MORET SUR LOING CEDEX - FRANCE

Principal Investigator L. Crétinon

This report describes research sponsored by EPRI.

This publication is a corporate document that should be cited in the literature in the following manner:

Guidance for Aging Management of Instrumentation and Control (I&C) Circuit Cards and Components Based on Électricité de France (EDF) Experience. EPRI, Palo Alto, CA: 2010. 1022246.

#### **ABSTRACT**

This report deals with the good practices recommended by Electricité de France (EDF) Research & Development (R&D) concerning the maintenance of Printed Circuit Boards (PCB) used in nuclear power plants. It is shown than the procedure developed by EDF R&D is mainly based on visual inspection and deep physical analysis (destructive analysis of components and PCB) in order to evaluate the aging of a PCB. Some specific tools (dedicated to the aging evaluation of electronic components such as capacitors, optoelectronic couplers, thyristors and other power components) can be developed and are described here. When the aging status is determined, it is then possible to define critical electronic components and/or boards. The aging of these boards has to be carefully followed and when necessary preventive maintenance can be performed. Some examples of this are given.

Finally this report discusses some ideas in order to mitigate the stressors that may affect the remaining life-time of PCBs. The main stressors discussed are handling (including electrostatic discharges), environment conditions (pollution, temperature, humidity) and electrical overloads. For each stressor some good practices are given. A special focus is made on storage conditions.

#### REPORT SUMMARY

Circuit cards of instrumentation and control (I&C) systems in nuclear power plants are designed for several decades of use and are inevitably subject to aging. Aging can result in the appearance of numerous failures, or it may lead to a drift of the electrical properties of a component, which can have different levels of critical consequences depending upon the systems concerned. The risk of such failures increases with circuit card age. Described here are several good practices to inspect for aging effects and to mitigate external factors that lead to premature aging of circuit cards and their components.

#### **Background**

Circuit card failures are a significant contributor to nuclear power plant forced outages and system failures, leading to undesirable plant transients and reduced power operation levels. These failures cost the nuclear power industry many millions of dollars annually due to lost revenue, replacement power purchases, increased labor, and unnecessary challenges to plant safety systems. Aging issues are raising serious concerns that the number of forced outages and system failures caused by circuit cards and their components will increase significantly over the life of the plant.

Operating nuclear power plant owners are expecting longer lifetimes with high reliability from existing I&C systems. An understanding of circuit card aging is critical to achieving such expectations. The anticipation of failures of I&C systems and the decision for refurbishing or reengineering a system are directly related to the consequences associated with aging of circuit cards and components. An appropriate monitoring of aging, therefore, allows for an optimized maintenance policy and, in the end, for an extension of I&C system life expectancy. This report identifies approaches to better understand aging of circuit card components and to use that knowledge to better assess their remaining useful life.

#### **Objective**

To provide good practices and other valuable information based upon observations and analyses of circuit card and component aging effects on Électricité de France (EDF) plants.

#### **Approach**

The project team reviewed information supported by observations of a few thousand failed and abnormal circuit cards and components from EDF fleets of 30 900-MWe and 20 1300-MWe nuclear power plants. The team applied the information from these observations to gain important insight on the aging of circuit cards and their components. Based on this review, the team identified good practices for aging inspections and monitoring as well as limiting of external factors that contribute to aging.

#### Results

Visual inspection is a valuable tool to understand the current state of the circuit card and its components. This report provides guidance on the appropriate order of inspections, required tools and criteria for inspections, limitations of visual inspections, and examples of defects. In order to gain more detailed understanding of the aging of circuit cards and components, nondestructive off-line testing approaches as well as destructive techniques are discussed.

The report provides guidance on analyzing results from visual, nondestructive, and destructive techniques to develop assessments of the aging of circuit cards and components. Such assessments can be used to establish lists of components that are sensitive to aging and components that are not likely to reach their expected useful life. Once sensitive components are identified and the causes and rates of operational failures are known, it is possible to set up an effective policy of judicious preventive replacement to limit the number of failures.

The results of this report can be used by utilities to increase their understanding of aging mechanisms and the attendant consequences based on plant operating experience. The good practices can also be used to modify plant procedures and practices in order to help reduce external factors that contribute to aging. Finally, the tools and techniques for monitoring, analysis, and prediction of aging can be used to improve maintenance practices and thereby extend the life of circuit cards and the I&C systems that rely on them.

#### **EPRI Perspective**

EDF and EPRI have documented considerable circuit card failure and aging operating experience. They have defined a set of good practices for assessing the aging of circuit cards and electronic components in two reports, available as a set under EPRI order number 1008166: Collected Field Data on Electronic Part Failures and Aging in Nuclear Power Plant Instrumentation and Control (I&C) Systems (EPRI report 1003568, 2002) and Guidelines for the Monitoring of Aging of I&C Electronic Components (1008166, 2004). The current report, 1022246, describes the results of more recent work; additional good practices will be presented in another report to be developed in 2011. Material from 1022246 will also be incorporated into an ongoing EPRI companion project to develop circuit card life-cycle management guidelines, slated for publication in 2011.

#### **Keywords**

Circuit Cards

Circuit Boards

Aging

Failure Analysis

Electronic Components

Reliability

Maintenance

Visual Inspection

## **CONTENTS**

| 1 AGING AND LOSS OF RELIABILITY OF PRINTED CIRCUIT BOARDS     | 1-1  |

|---------------------------------------------------------------|------|

| 2 PERIODIC VISUAL INSPECTIONS OF PRINTED CIRCUIT BOARDS       | 2-1  |

| General Principle                                             | 2-1  |

| Tools Required                                                | 2-1  |

| Criteria Assessed During Visual Inspection                    | 2-2  |

| Examples of Observable Defects                                | 2-6  |

| Overall Appearance of the Printed Circuit                     | 2-6  |

| State of the Solders                                          | 2-7  |

| Faults Observed on Components                                 | 2-8  |

| Faults Observed on Connectors                                 | 2-9  |

| EDF Inspection Approach                                       | 2-9  |

| Limitations of the Technique                                  | 2-10 |

| Summary                                                       | 2-12 |

| 3 ADDITIONAL INSPECTION APPROACHES FOR PRINTED CIRCUIT BOARDS | 3-1  |

| Off-Line Analyses                                             | 3-1  |

| Difficulties of On-Line Analyses                              | 3-1  |

| Capacitors                                                    |      |

| Thyristors                                                    | 3-3  |

| Optoelectronic Couplers                                       | 3-5  |

| Other Power Components                                        | 3-6  |

| Complex Active Component                                      | 3-7  |

| Destructive Testing of Components                             |      |

| Principle                                                     |      |

| Extrapolation to the Anticipation of Aging                    |      |

| Coverage Ratio and Rate of False Failures                     |      |

|                                                               |      |

| Actions to be Taken After a Failure Analysis                   | 3-14 |

|----------------------------------------------------------------|------|

| Recommendations for the Use of Failure Analysis                | 3-15 |

| Monitoring Reports from PCB Repairers                          | 3-15 |

| Summary                                                        | 3-15 |

| 4 TECHNOLOGY WATCH OF OPERATING EXPERIENCE IN OTHER INDUSTRIES | 4-1  |

| 5 CRITICALITY OF COMPONENTS AND PREVENTIVE MAINTENANCE         |      |

| Components Sensitive to Aging                                  |      |

| Sensitive Boards and Systems                                   |      |

| Preventive Replacement and Partial Renovation                  |      |

| 6 MITIGATION OF EXTERNAL FACTORS                               | 6-1  |

| List of the Stressors Concerned                                | 6-1  |

| Handling                                                       | 6-1  |

| Impact of the Human Factor                                     | 6-1  |

| General Recommendations                                        | 6-1  |

| General Recommendations                                        | 6-4  |

| Ambient Conditions                                             | 6-7  |

| Types of Protections                                           | 6-7  |

| Types of Varnish                                               | 6-8  |

| Conclusions                                                    | 6-10 |

| Electrical Overloads                                           | 6-10 |

| Operating Temperature                                          | 6-11 |

| Special Case of the Storage of Electronic Components           | 6-11 |

| Conclusions about the Mitigation of Stressors                  | 6-12 |

| 7 ASPECTS TO BE DEVELOPED                                      | 7-1  |

| Environment Monitoring Micro-Sensor                            | 7-1  |

| On-Line Analysis Techniques                                    | 7-1  |

| Early Warning Indicators of Aging                              | 7-2  |

| 8 CONCLUSIONS                                                  | 8-1  |

| 9 REFERENCES                                                   | 9-1  |

## **LIST OF FIGURES**

| Figure 2-1 Endoscope used for inspections                                                                                                                                                                                                                                                                               | 2-2  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2-2 Faults in overall appearance of the PCB: (left) bubbles in the resistor (right) severe accumulation of dust likely to lead to short-circuits.                                                                                                                                                                | 2-6  |

| Figure 2-3 Faults in overall appearance of the PCB: (left) electromigration between two tracks of the PCB and (right) overheating of diodes (originally blue) leading to                                                                                                                                                |      |

| overheating of the PCB.                                                                                                                                                                                                                                                                                                 | 2-6  |

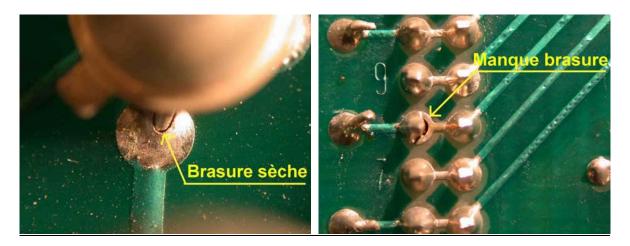

| Figure 2-4 Faults on the solders (left) dry solder and (right) lack of solder                                                                                                                                                                                                                                           | 2-7  |

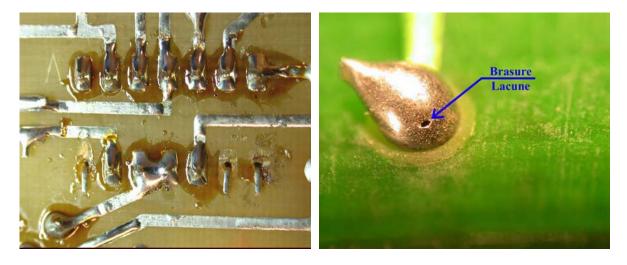

| Figure 2-5 Faults on solders (left) residue of flux not cleaned and (right) lack of solder                                                                                                                                                                                                                              | 2-7  |

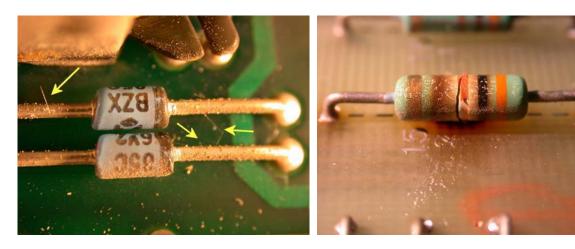

| Figure 2-6 Examples of faults on components: (left) whiskers on BZX diodes and (right) crack of the package of a resistor.                                                                                                                                                                                              | 2-8  |

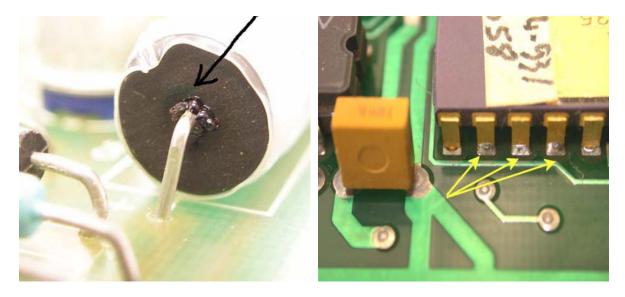

| Figure 2-7 Examples of faults on components: (left): leak from an electrochemical capacitor and (right) solders on a component with a gold finish not previously stripped.                                                                                                                                              | 2-8  |

| Figure 2-8 Examples of faults on connectors: (left) connector fouled and damaged and (right) deep scratch of approximately 5 µm that reveals and damages the coating of nickel under the superficial protective coating of gold, which could result in the oxidation of the contact.                                    | 2-9  |

| Figure 2-9 (left) female HE9 connector corroded and housing damaged (observed by endoscope) and (right) signs of organic pollution (observed in UV light) on a male HE9 connector.                                                                                                                                      | 2-9  |

| Figure 2-10 Example of an electronic circuit board for which visual inspection is difficult                                                                                                                                                                                                                             | 2-11 |

| Figure 3-1 Modeling of the frequency behavior of a capacitor                                                                                                                                                                                                                                                            | 3-2  |

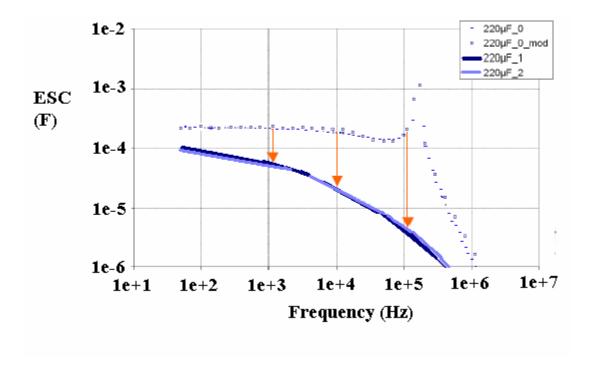

| Figure 3-2 Frequency response for frequencies between 50 Hz and 1 MHz of a non-defective electrochemical capacitor of 220 µF (top curve with its model once the parameters of the model are identified) and two defective capacitors of the same capacitance. The arrows represent the changes to the curve with aging. | 3-3  |

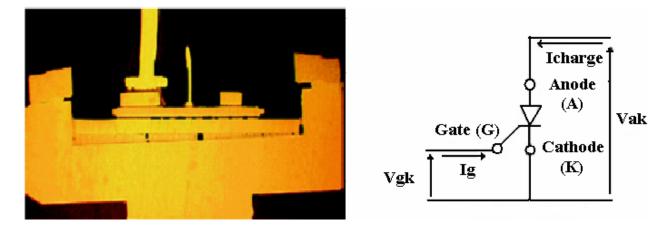

| Figure 3-3 (left) cross-sectional view of a thyristor and (right) electrical circuit diagram                                                                                                                                                                                                                            | 3-4  |

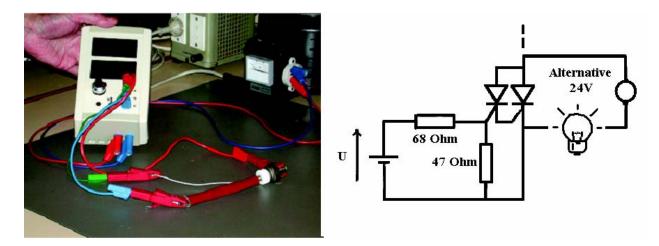

| Figure 3-4 (left) Measuring instrument developed for measuring the aging of thyristors, and (right) circuit diagram with a LED which is used to indicate the switching of the thyristor.                                                                                                                                | 3-5  |

| •                                                                                                                                                                                                                                                                                                                       |      |

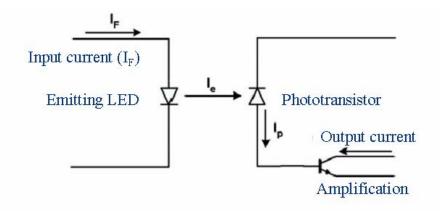

| Figure 3-5 Circuit diagram for an optoelectronic coupler.                                                                                                                                                                                                                                                               | 3-5  |

| Figure 3-6 Example of a tool used to measure the ratio between output current and input current.                                                                                                                                                                                                                        | 3-6  |

| Figure 3-7 Aging of the microstructure of solders (left): solder less than 5 years old: (right): solder after aging for 35 years [11].                                                                                                                                                                                  | 3-10 |

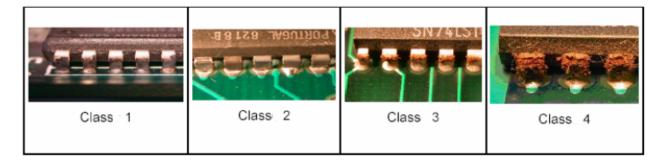

| Figure 3-8 SEM images of the chip of a Texas Instrument SN74LS244N                                                                                                                                                                                                                                                      |      |

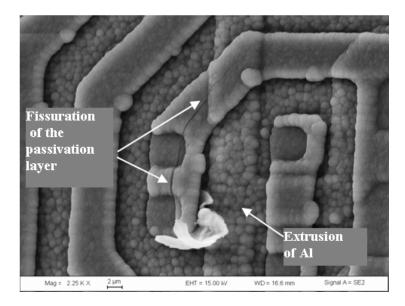

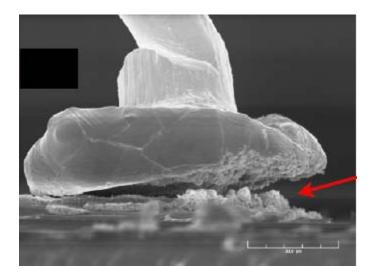

| Figure 3-9 Lack of metal, effects of electromigration on the chip of a RS flip-flop                                                                                                               | 3-12 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3-10 Presence of cracking and extrusion of aluminum on the chip of a SRAM memory.                                                                                                          | 3-13 |

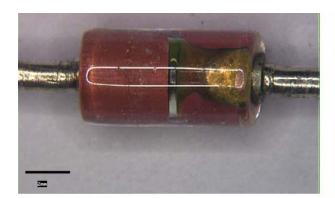

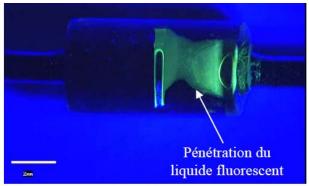

| Figure 3-11 (left) BZX85C diode in white light (right) and in ultraviolet light after being placed in a fluorescent liquid under pressure                                                         | 3-13 |

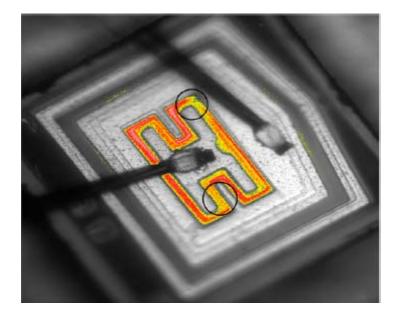

| Figure 3-12 EMMI image of the chip of an almost defective 2N2222 transistor                                                                                                                       | 3-14 |

| Figure 5-1 Various stages of corrosion                                                                                                                                                            | 5-2  |

| Figure 5-2 Separation of a gold connection wire initially on the aluminum pad of a 2N3019 transistor                                                                                              | 5-2  |

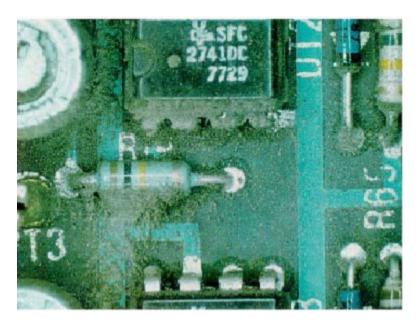

| Figure 6-1 Example of a severely fouled board for which cleaning is required                                                                                                                      | 6-2  |

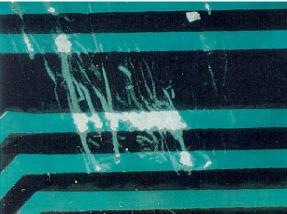

| Figure 6-2 (left) Examples of packaging for transporting the boards on site, (right): track of a printed circuit laid bare due to two boards rubbing against each other during                    |      |

| transport                                                                                                                                                                                         | 6-3  |

| Figure 6-3 Connector unplugged while energized.                                                                                                                                                   | 6-3  |

| Figure 6-4 Potential strip damaged by the use of inappropriate tools                                                                                                                              | 6-4  |

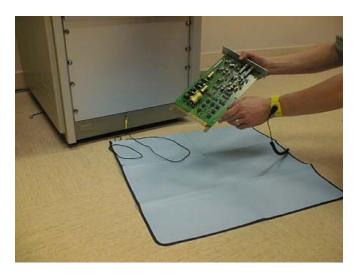

| Figure 6-5 Example of partial damage to a transistor following an electrostatic discharge.  The component is still functional but the thickness of the oxide is so reduced that failure is close. | 6-5  |

| Figure 6-6 Work station for the inspection of printed circuit boards: the operator is connected to the mat which is connected to the grounded frame of the cabinet                                | 6-6  |

| Figure 6-7 Carbon black anti-ESD protection devices                                                                                                                                               | 6-7  |

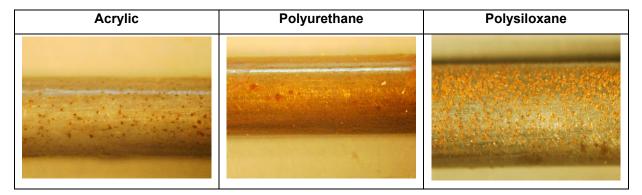

| Figure 6-8 Comparison of the permeability to corrosion of three varnishes (acrylic, polyurethane [orange] and polysiloxane): we observe less pitting in polyurethane-based varnishes.             | 6-10 |

|                                                                                                                                                                                                   |      |

### **LIST OF TABLES**

Table 6-1 Sensitivity of various component technologies to electrostatic discharges......6-5

# **1**AGING AND LOSS OF RELIABILITY OF PRINTED CIRCUIT BOARDS

The printed circuit boards of instrumentation and control systems in nuclear power plants are designed to be used for several decades and are inevitably subject to aging. Despite being used in a relatively protected and stress-free environment, they are continuously subjected to external factors which will alter their electrical characteristics internally. Also inevitably and for fundamentally thermodynamic reasons (completely independent of the operator), electronic components, printed circuits, etc., will age, if only because of ambient temperature which, over period of 30 to 40 years, is no longer a negligible factor. Aging does not necessarily result in the appearance of numerous failures. It may simply lead to a drift of the electrical properties of a component (longer response time, reduction in the gain of a transistor, modification of the value of the capacitance of a capacitor, etc.) which are, depending on the systems concerned, more or less critical and more or less acceptable. Nevertheless, in all cases, the risk of failure increases with aging.

Although the fundamental causes of aging and loss of reliability are physical in nature, we must try to limit the effects of aging. Without being able to prevent printed circuit boards from aging, we shall try to slow aging as much as possible. This involves creating an appropriate policy on maintenance and MRO (maintain, repair and operation). Although based on a relatively old technology in general, the instrumentation and control systems of nuclear power plants remain potentially sensitive to aging if we include the time factor. For example, active components (e.g., thyristors, transistors) manufactured in the 1990s, provided that they were produced according to the state of the art of the time, are considered to have a life span of 50 years, or even more. These life spans, albeit long, roughly correspond to the life spans of nuclear plants. Therefore, while the aim is to extend the life span of instrumentation and control systems to match the entire life span of the plant, the margin between the theoretical life span of the component and its actual life may be quite small. That is why we should adopt a number of good practices to limit the attacks on printed circuit boards, be capable of assessing their aging (if only to know whether new practices should be defined, if the system has to be renovated, etc.).

Good practices are governed by a certain number of essentials. As mentioned above, their main aim is to limit any external factors and seek to extend the life span of equipment, while maintaining an optimum level of reliability. The good practices may be classified into three major groups: those concerning the monitoring of aging (types of analysis, frequency, etc.), those concerning taking account of such aging and, finally those concerning the mitigation of external factors.

The purpose of this report is to describe the good practices introduced by Electricité de France (EDF) and covers, in particular, the recommendations and techniques developed by EDF

46BAging and Loss of Reliability of Printed Circuit Boards

Research and Development (R&D), which is responsible within EDF for the development of the methodologies and the definition of good practices.

Chapters 2 and 3 of this report describe good practices in terms of the inspection for and the monitoring of aging to assess the remaining useful life. Chapter 2 discusses visual inspections, which constitute one of the two main areas of research into aging. Chapter 3 concerns, among other things, additional means including a description of non destructive testing equipment for specific components and destructive testing, the second main aspect for obtaining a detailed knowledge of the state of aging.

Chapter 4 of this report discusses into the usefulness of a technology watch of operating experience in other industries and how to account for it in assessing remaining life.

Chapter 5 discusses establishing a detailed inventory of the components in instrumentation and control systems that are affected by aging and those that are likely to not meet their design life. There is given an approach to determine, based on the aging of electronic components, modules and even critical systems, which should be monitored in particular.

Chapter 6 discusses the possibility of limiting the impact of external factors on components, modules and systems previously shown to be sensitive to aging for all usual factors such as temperature, humidity, pollution, etc.

Finally, Chapter 7 reviews several aspects being developed to improve maintenance practices still further through better analysis and prediction of aging to find better approaches for maintaining operational conditions.

## 2

# PERIODIC VISUAL INSPECTIONS OF PRINTED CIRCUIT BOARDS

#### **General Principle**

At EDF R&D, one of the two main aspects concerning the monitoring of the aging of the printed circuit boards of instrumentation and control systems lies in the analysis of direct visual inspection of printed circuit boards (PCB). The approach, which is applicable to all electronic circuit boards, consists in reviewing a series of criteria, which may be observed visually and reveal the state of aging of the electronic circuit board. In order to limit the inspection time, the observation should focus on points which, in the light of experience, the operator has decided are critical. The inspector reviews for abnormalities the following in the indicated order:

- Overall appearance of the printed circuit board.

- State of solders.

- Faults observed on components.

- Faults on connectors.

The following points should also be examined, depending on the components concerned and the history of the board:

- The state of any repairs.

- Specific visual inspection of relays.

#### **Tools Required**

The inspections described here are visual, but this does not mean that no special tools are required. For optimum results, it is useful to have the following equipment available:

- A 5 to 10 magnifier.

- One directional source and another circular source of white light.

- A source of ultra-violet light.

- A microscope with higher magnification, typically at least x 20.

- An endoscope with a small diameter (see Figure 2-1), capable of observations of the back of

instrumentation and control system racks (capable of transmitting both white light and

ultraviolet radiation).

• An IPC A 610 index D guide (latest version, incorporating RoHS assemblies). The standard IPC A 610 specifies the acceptance criteria for printed circuit boards leaving the assembly line. It comprises three levels of requirements: the first concerns domestic electronic consumer goods for which high reliability and long life span are not essential. On the other hand, class 3 is the most restrictive and is intended for application in safety-related, military applications, etc. The instrumentation and control system falls, quite naturally, into class 3. Nevertheless, some criteria may be used for class 2. EDF R&D uses this standard prior to the creation of its own frame of reference.

Figure 2-1

Endoscope used for inspections

We must be very cautious as to the level of magnification used during inspections (using a magnifier or microscope). Magnifications greater than x 10 should be used sparingly and only to confirm a fault (and not to find it). Relatively high levels of magnification may only be used to detect faults on highly integrated boards. Indeed, by magnifying a specific point, it is always possible to observe a fault. Let us take for example, the case of a solder. The acceptance criterion generally accepted for a tin-lead solder (Sn63Pb37) is that it should be smooth and shiny, as laid down in standard IPC A 610. Now magnification of x 10 or more is enough to reveal a granular surface appearance of solders, especially when they are made by hand. It is also easy to reveal the presence of cracks not visible to the naked eye. All these aspects may lead an inexperienced inspector to classify such solders as unsatisfactory or spend a long time checking whether all the minor faults observed comply with class 3 of standard IPC A 610 or not.

#### **Criteria Assessed During Visual Inspection**

Each of the main categories described above is then divided up into a large number of criteria, given in detail in the remainder of this chapter. Therefore, when checking the overall appearance of the printed circuit board, the PCB should be checked for the presence or lack of presence of the following:

- Overheating.

- Buckling of the board.

- Delamination or even cracking of the printed circuit.

- Severe accumulation of dust (leading, in particular, to a bridge of dust between two component pins, which may result in a short-circuit if the dust conducts).

- Deposition of unexpected particles.

- Residues of alloy used for solders outside the pads for solder paste.

- Integrity of the coat of varnish for tropicalized or varnished boards.

- Separation of tracks and mounting pads for electronic components.

- Oxidation or corrosion of the conductors on printed circuits (visible especially for copper tracks).

- Obvious design faults of printed circuit boards.

In so far as the "state of solders" is concerned, the criteria to be taken into consideration are as follows:

- Presence of dull solders (and, therefore, carried out badly).

- Presence of accidental alloy bridges between two solders.

- Quality of the solders (lack of solder, sufficient rise of the solder on the component, form of the soldered joint, etc.) according to standard IPC A 610 index D.

In the category "faults observed on components", special attention should be paid to the following points:

- Presence of whiskers on the pins of components.

- Corrosion of the pins or casings of components.

- Signs of impact, cracking of casings (to be checked for hermetically sealed components).

- Overheating of components.

- Leaks of electrolyte from electrochemical capacitors.

- Components mounted incorrectly (particularly in terms of the earthquake qualification of heavy components which should be maintained by specific attachments).

- Pins of bent components.

- Tin plating on gold plated pins: making a solder on components with gold plated pins will lead to the formation of gold-based intermetallic compounds in the solder. If the gold content in the final solder is too high (1% may suffice), the solder will have a very short life span. If the lead of the component is coated with a simple flash of gold, there will not be enough gold in the solder for the danger limit to be reached. But visually, it cannot be seen. According to the precaution principle, the components with gold plated pins should, therefore, not be used.

The items to be observed in the category "faults on connectors" mainly concern card-edge connectors. We separate inspections of the male part (on the printed circuit) from those of the female part. The male part is more accessible, since the female part is located at the back of a cabinet of the instrumentation and control system. For the male part, the inspector should observe the following points:

- Presence of inorganic pollution (observation carried out in white light).

- Presence of organic pollution (observation carried out in ultra-violet light which reveals the presence of organic pollutants) [1-2].

- Signs of corrosion and/or oxidation.

- Presence of scratches on the tracks and estimation of their depth.

- Separation of the tracks by mechanical damage.

- Signs of arcing.

- Deformation of the indexing pin (if appropriate).

For the female part of the connector, the inspection involves assessing the following criteria, observed by endoscope:

- Observation of the vacuum spacing (directly visually by endoscope or using a calibrated camera).

- Signs of corrosion and/or oxidation.

- Presence of inorganic pollution (in white light).

- Presence of organic pollution (in ultra-violet light).

- Presence of scratches on the clips (note: this observation is very difficult owing to reflections from the external light source required).

- Damage to the plastic casing of the connector (base).

Each of these criteria forms an integral part of all inspections. If necessary, the inspection may be completed by an assessment of the compliance of the repairs with the frame of reference of IPC A 610 version D level 3. Even if it only covers the quality of assemblies, it is considered that a repair should not be worse than manufacture itself. One has also to refer to two other standards: IPC 7711 and IPC 7721). The relay may also result in specific, albeit limited inspections (in particular, visual inspection on a relay with a metal cover is meaningless).

Each of the criteria discussed above gives rise to an assessment with 4 levels of severity. These levels are "aesthetic", "caution", "alert" and "critical". They are defined as follows:

- "Aesthetic" means that a fault has been detected but that it has no impact on the long-term operation of the PCB examined (for example, the presence of dust in relatively small quantities or superficial scratching of the casing of a component not affected by oxidation).

- "Caution" means that a fault has been detected and if nothing is done, a failure is probable before the end of the board's life span (typically after more than 10 or 15 years).

- "Alert" means that a fault has been detected and it leads to a risk of failure or reduced reliability of the board within less than 10 years.

- "Critical" means that a fault has been detected and a failure is imminent or the failure is already present.

In theory, the four scores may be assigned to any of the observation criteria. In practice, certain faults are so serious that they cannot be "aesthetic" or even "caution". For example, for cardedge connectors, the vacuum space between two clips of the same pair determines the contact force and, therefore, the contact resistance. When we detect visually that the gap is too wide, this means that the resistance value is already outside specifications (visual acuity is not sufficient to observe behavior at the limit of specifications). Accordingly, the inspector will have no other choice but to assign an "alert" or "critical" score it he detects such a fault. On the other hand, certain faults may never be "critical" such as, for example the presence of dust on the board.

Following the assessment of all the criteria described above, a final score is given to the PCB examined. It also has four levels possible:

- S ("satisfactory"): no criteria call into question the operation of the board under normal conditions for the next 20 years,

- M+ ("average +"): several faults may eventually reduce the reliability of the module and lead to failures. Repairs or backfitting are not essential,

- M- ("average -"): without corrective action, the electronic circuit board has a life expectancy of less than 10 years,

- NS ("unsatisfactory"): the board is far from the standard expected and a failure is imminent if no corrective action is taken. Such boards are generally withdrawn from service temporarily to await corrective action.

Finally and if necessary, the inspector makes recommendations concerning corrective action that could improve the board's score. This may involve cleaning certain parts of the board, the preventive replacement of a component, the failure of which is considered to be imminent, the repair of tracks of the printed circuit, etc.

#### **Examples of Observable Defects**

Figures 2-2 through 2-9 illustrate some of the faults which may be observed during these visual inspections. Naturally, the list is by no means exhaustive.

#### Overall Appearance of the Printed Circuit

Figure 2-2

Faults in overall appearance of the PCB: (left) bubbles in the resistor (right) severe accumulation of dust likely to lead to short-circuits.

Figure 2-3

Faults in overall appearance of the PCB: (left) electromigration between two tracks of the PCB and (right) overheating of diodes (originally blue) leading to overheating of the PCB.

#### State of the Solders

Figure 2-4

Faults on the solders (left) dry solder and (right) lack of solder.

Figure 2-5

Faults on solders (left) residue of flux not cleaned and (right) lack of solder.

#### Faults Observed on Components

Figure 2-6 Examples of faults on components: (left) whiskers on BZX diodes and (right) crack of the package of a resistor.

Figure 2-7

Examples of faults on components: (left): leak from an electrochemical capacitor and (right) solders on a component with a gold finish not previously stripped.

#### Faults Observed on Connectors

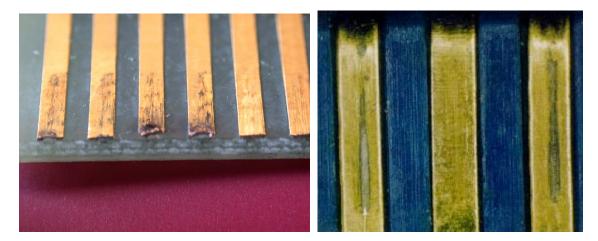

Figure 2-8

Examples of faults on connectors: (left) connector fouled and damaged and (right) deep scratch of approximately 5 µm that reveals and damages the coating of nickel under the superficial protective coating of gold, which could result in the oxidation of the contact.

Figure 2-9 (left) female HE9 connector corroded and housing damaged (observed by endoscope) and (right) signs of organic pollution (observed in UV light) on a male HE9 connector.

#### **EDF Inspection Approach**

Inspections are carried out mainly by EDF R&D when preparing for the ten-yearly in-service inspections, as part of an approach known as "Monitoring of the aging of instrumentation and control systems" (OVCC in French) and currently applied to 900-MW units, on the one hand and those of 1300 MW, on the other. This approach is not yet in place for N4 units (1450 MW). The main instrumentation and control systems are inspected as follows, boards are chosen at random from each of the systems on various sites (typically at least 3 sites, one of which is a seaside site and one a river site, in order to exploit data from different environments). Therefore, on a

campaign of type OVCC (900 MW or 1300 MW), several hundred of boards are inspected individually. The data obtained are then collated for each system (for example "reactor protection") which gives a good representation of the state of aging of printed circuit boards and forecast of their residual life span. These results provide a basis for making decisions as to whether or not to renovate an instrumentation and control system either partially or totally during ten-yearly in-service inspections.

It is clear that this approach, which is followed systematically every ten years, can only be limited in terms of scope (therefore to the OVCC in preparation for the third ten yearly in-service inspection of 1300-MW units, approximately 2000 boards have been examined. This number is certainly high but, when compared to the total number of printed circuit boards for all the 1300-MW facilities, it remains relatively modest). That is why it was decided to transfer visual inspection skills partially to the nuclear sites. EDF R&D has established training courses for site employees since 2010. The aim in the long term is to ensure that all boards handled for the purposes of maintenance are inspected. The results of inspections are subject to reports sent to EDF R&D which analyzes them, thus obtaining a much finer overall view of the state of aging than that determined following OVCC.

It must also be noted that this visual inspection technique is also used for trouble-shooting, spurious or transient faults. It does not only concern nuclear instrumentation and control systems, but is also very efficient for all instrumentation and control systems (typically for more conventional transmission, distribution or production installations (hydraulic, fossil fuel, etc.]), which enables inspectors to perform inspections often and, therefore, improve their expertise.

#### **Limitations of the Technique**

As mentioned throughout the previous sections, this method of assessing the state of aging of printed circuit boards is based only on visual inspections, occasionally assisted by optical magnification or special light sources. It is not yet intended to use sources such as X-rays, which would enable us to see through the packaging of the electronic components, for reasons of safety of instrumentation and control systems (this is currently under review). Accordingly, only external faults and aging (or internal faults with external consequences, such as severe overheating for example) can be detected. In particular, visual inspection reveals nothing about faults such as thick intermetallic compounds on bonding wires on chips, the local overheating of chips, the presence of damage due to electrostatic discharges (ESD) inside the component, etc. The same situation applies to multi-layer boards. In some cases there are no components in the internal layers, in other cases there are and these can not be observed visually. Lack of observability occurs with the recent technologies SiP (systems in package) and SoC (systems on chip). One can also find this problem with hybrid integrated circuits. For all such hidden faults, qualified as internal faults, other often destructive techniques have to be used and shall be described in Chapter 3.

Another limitation is due to the fact that the inspector does not have visual access to all the components with the right angle of view. He may be hampered by the presence of a solid component beside the one he wishes to examine. Therefore, lighting is not optimal and he is likely to miss certain faults (this is often the case for whiskers).

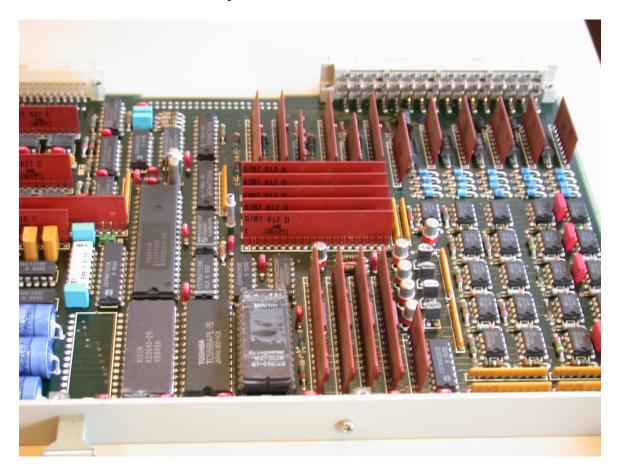

The third limitation to be mentioned is due to the density of metal components on the boards. While packages are often made of non-reflective plastic, this is not true of pads, solder and the component leads. These metal surfaces will generate reflections which will also hamper observations. Figure 2-10 gives an example of a highly integrated board with a high density of metal leads, which makes visual inspection difficult.

Figure 2-10 Example of an electronic circuit board for which visual inspection is difficult.

By combining these two points, it may be noted that the more a board is integrated, the more visual inspection is inaccurate.

Visual inspection with magnifiers is highly appropriate for older technologies (typically for systems put into service from the 1970s to the 1990s, which are the vast majority of the instrumentation and control systems in French nuclear power plants), because these systems have the following characteristics:

- There are no SMC (surface mounted components) or (in the worse case) BGA (Ball Grid Array) on the PCB.

- The density of components remains low.

- The number of ICs (integrated circuits) remains small.

47BPeriodic Visual Inspections of Printed Circuit Boards

• The PCB is not a multilayered board.

Newer technologies for systems that do not meet the above characteristics need more robust capabilities. These more robust capabilities are a current research issue at EDF R&D.

#### **Summary**

The visual inspection technique is the basic technique developed and used by EDF R&D for estimating the aging of electronic circuit boards and anticipating their residual life span. It is used very extensively but, while it gives relatively complete results that are easy to obtain, it is not sufficient for fine monitoring of aging and for defining the required preventive maintenance. That is why it is complemented by other more extensive inspections, which are described in the next chapter.

## 3

## ADDITIONAL INSPECTION APPROACHES FOR PRINTED CIRCUIT BOARDS

#### **Off-Line Analyses**

#### Difficulties of On-Line Analyses

In order to be able to carry out the right maintenance operations at the right time without affecting the operation and reliability of boards by excessive handling (see Chapter 6), on-line diagnostics tools should be available for continuous analysis in real time. On-line analysis also enables us to anticipate failures and eliminates the need to carry out inspections requiring handling during the shutdown of the system concerned.

Nevertheless, it is very difficult to carry out such analyses. Indeed, the boards currently in service were not designed with on-line testing in mind. Adding a system for monitoring the board during operation will likely lead to disturbances of varying degrees on the board being monitored. If adding monitoring, it should be shown that in all possible cases, including incorrect operation of the monitoring system, operation of the electronic circuit board concerned is not affected. Therefore, if we wish to take an electrical measurement, we must ensure that there are no leak currents strong enough to alter the electrical levels of neighboring components (for example, change one bit in a memory, change of state of a diode, etc.). This is extremely time-consuming and explains why no good on-line measurements are currently available, with the exception of periodic testing. However, the purpose of periodic testing is to reveal any failures or even marked aging but in no case reveals signs of aging.

Furthermore, it is very difficult to use certain investigation techniques on site such as X-ray imaging methods, multipoint electrical testers, etc.

Therefore, it is simpler to look for off-line analysis solutions to overcome the problems raised here.

#### **Capacitors**

The passive components that pose the most problems from aging by far are capacitors of all types. This means not only electrochemical capacitors, but also ceramic and tantalum capacitors.

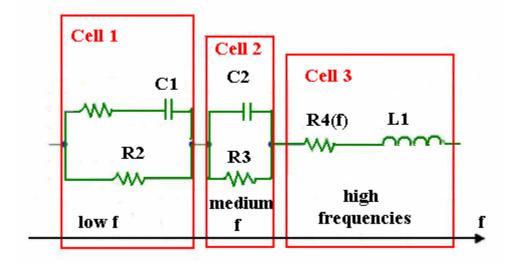

In all these cases, EDF R&D has developed a technique for the analysis of aging based on the impedance spectroscopy [3-5]. For this, the behavior of a capacitor was modeled by breaking it

down into an inductor, several resistors and capacitances in series or in parallel as shown on Figure 3.1. The model consists of three blocks, each of which corresponds to a given frequency range. At low frequency; cell No. 1 is used to characterize dielectric losses and insulation resistance at low frequency. It is important to note that resistance R1 depends on frequency. Cell No 2 reveals faults on the interfaces of the dielectrics at medium frequency. Cell No. 3 (high frequency) is a good indicator of the state of internal connections. For a more detailed model, we can include the dependency of resistance R4 on frequency.

Figure 3-1 Modeling of the frequency behavior of a capacitor.

Once this model is established, measurement of aging involves the analysis of the spectral response of the capacitor in a range from 40 Hz to 5 MHz. After the spectrum has been recorded, we must identify the values of each of the parameters of the model by simulation. Specific points (such as the value of resonance frequency) are used to determine the parameters of interest, as shown in [3], quite quickly.

In many cases, the values of the parameters of the equivalent diagram are used to determine the state of aging of capacitors, particularly for electrochemical capacitors and tantalum capacitors, for which the relatively simple criteria may be used:

• For electrochemical (aluminum) capacitors, we should monitor, in particular, changes to parameter R4 and parameter C1, which have proven to be early aging indicators. Aging is also indicated well by the measurement of the frequency of equivalent series capacitance, as shown on Figure 3-2. With aging, resonance is reduced and the appearance of the frequency response curve of equivalent series capacitance is greatly altered.

Figure 3-2 Frequency response for frequencies between 50 Hz and 1 MHz of a non-defective electrochemical capacitor of 220  $\mu F$  (top curve with its model once the parameters of the model are identified) and two defective capacitors of the same capacitance. The arrows represent the changes to the curve with aging.

• For tantalum capacitors, the studies show that there is no significant variation in parameters C1 and R4. On the other hand, the study of cell No. 2 (intermediate frequencies), characterizing the interface oxide reveals a change to parameters C2 and R3.

It is important to note that these measurements are non-destructive and that the study of the frequency response of the other passive components (resistors and coils) also gives good results, which are less easy to exploit than those for the capacitors, but which enable us to detect the first signs of aging.

These measurements should be carried out on a regular basis but may be a year or more apart. Any changes to the mechanisms are quite slow.

#### **Thyristors**

It is also possible to anticipate the aging of certain power components, such as thyristors [6], quite simply. According to the literature [6], thermo-mechanical aging due to power cycles is the main aging mechanism. It results in damage to the blocking characteristics. This is not the case for thyristors studied by EDF R&D (thyristors TS1235, TK1120 and TK12 [switching thyristors]). Indeed, no correlation has been found between the number of power cycles and any electrical drift observed. Accordingly, the only electrical characteristic of the thyristors which varies after 20 years is the trigger current threshold. Indeed, given their design, such thyristors

are not subject to thermo-mechanical aging. Figure 3-3 shows a cross sectional view of a thyristor and the operating diagram.

Figure 3-3 (left) cross-sectional view of a thyristor and (right) electrical circuit diagram.

To determine the aging of such thyristors, we should; therefore, measure the trigger current. Studies have shown that the variation of trigger current is generally accompanied by significant drift of the holding current. Accordingly, the thyristors go out after suppression of the command. Similarly, high leak currents appear. Several causes may explain the variation in the trigger current during aging. The two main causes are:

- A manufacturing fault, such as the misalignment of the cathode-trigger assembly.

- Aging of silicon, which may be natural.

Some of the other possible causes are:

- Misalignment of the cathode-trigger assembly.

- Ionic contamination of the die.

- Natural aging of silicon.

- Crack in the die.

- Damaged contacts at the die level.

- Corrosion of the contacts (at the die or at the component level).

A measuring instrument has been developed for the measurement of parameters  $I_g$  and  $V_{gk}$  at the same time. The principle of measurement is that the grid current is increased gradually until the thyristor switches. This illuminates a light emitting diode (see diagram on Figure 3-4). The trigger current is then measured and compared to the value given on the datasheet.

Figure 3-4 (left) Measuring instrument developed for measuring the aging of thyristors, and (right) circuit diagram with a LED which is used to indicate the switching of the thyristor.

#### Optoelectronic Couplers

Figure 3-5 Circuit diagram for an optoelectronic coupler.

Optoelectronic couplers are also components where, the aging is quite easy to detect early. The circuit diagram for an optoelectronic coupler is shown in Figure 3-5. The main causes of aging of optoelectronic couplers are as follows:

- A reduction in the efficiency of the light emitting diode which results in fewer photons passing between the light emitting diode and the phototransistor (resulting in a drop in output current).

- Opacification of the interface between the two diodes of the optoelectronic coupler, thereby reducing the number of photons reaching the phototransistor (resulting in a drop in output current).

• A reduction in the efficiency of the phototransistor and amplification. Here the number of photons reaching the phototransistor is correct but amplification is not sufficient, which reduces the output current.

In each of these cases, it would appear that the common parameter indicating signs of aging is the ratio between output current and input current. The measurement is made very simply by measuring an imposed input current and the resulting output current, at the same time. The instrumentation may be very simple. The tool used by EDF is shown in Figure 3-6 and is just connected to the optoelectronic coupler.

Figure 3-6

Example of a tool used to measure the ratio between output current and input current.

#### Other Power Components

As a general rule, aging indicators may be found on power components. We refer here to diodes and power transistors, thyristors, triacs and IGBT (main low voltage switch).

These components age in particular due to the fatigue of internal solders (typically the joints between the chip and the heat sink). Such fatigue is due to variations in temperature during power cycles and leads to the cracking in these joints. This mechanism will lead to an increase in the thermal resistance of the assembly and takes the form of an increase in the temperature of the casing. This parameter is determined by the use of an infrared thermal camera. The measurement may be made on-line.

On the other hand, if we wish to determine the state of aging (particularly problems due to the migration of ionic contaminants in the casing, resulting in an increase in leak currents and a drop in the maximum blocking voltage), this parameter should be measured by an electrical test. Now this measurement can only be made off-line. Even if it is very simple in terms of design, the component should be insulated to avoid any spurious measurements.

#### **Complex Active Component**

Until now only passive components and simple active components (components which sometimes incorrectly classified as passive components) have been discussed. The case of complex active components is more interesting since they perform more functions and generally play a key role in the operation of the board. However, it is very difficult to test (even off-line) active components on site. Indeed, the testers for them are particularly large and cannot be moved; such as multi-point testers for example. Only analysis in the laboratory enables the behavioral drift (and aging) of these components to be studied.

#### **Destructive Testing of Components**

#### **Principle**

To go further in the detection of aging and understanding of the causes of failures of components, the destructive testing of a component is the best technique currently available [7]. This form of testing consists of examining the active parts of components. It starts with the removal of the electronic component from its casing to examine its internal structure. Analysis is then much more detailed than from a simple visual inspection. This analysis approach continues with the use of various analysis techniques such as:

- X-ray examination: this non-intrusive, non-destructive technique is intended to see through plastic or metal casings and diagnose a certain number of obvious mechanical faults. We shall seek in particular to identify problems of loss of electrical or mechanical continuity (failure of the power supply wires of a coil in a relay, bonding wires not connected on a chip, etc.). This will guide our choice of complementary techniques for the rest of the analysis. In general, for relays and active components, X-ray examination is always the first step in the analysis of a failure.

- Observation in ultra-violet radiation: used mainly for contacts (relays, connectors, etc.), the ultraviolet light is used to reveal organic pollutants which act as a third body and affect the quality of the contact.

- Observation by scanning electron microscope (SEM): the SEM is the ideal tool for the analysis of failures. It provides, in particular, for the observation of small structures on chips and for the exploitation of micro sections. The surface observed is excited by a high energy beam of electrons and we are interested in back scattered or secondary electrons emitted by the surface being analyzed.

- Elementary analysis of components by energy dispersive X-ray spectroscopy (EDX): an EDX probe is associated with an SEM and is used to determine the nature of the elements present in its beam of electrons. The measurement is generally semi-quantitative. It is very useful for reverse engineering studies or for revealing the presence of unexpected elements (for example, it may be shown that the lead of certain electronic components is made of an iron-nickel alloy which will eventually corrode).

- Micro section: this is a cross section taken along a given axis in a component. The cross section (or micro section) is used, combined with an SEM, to make observations within the material itself. The disadvantage lies in the fact that the number of cross sections per

- component is necessarily limited and it is; therefore, useful to make first level diagnoses beforehand (by X-ray for example) to locate the fault as accurately as possible.

- Fourier transform infrared spectroscopy (FTIR): this technique is complementary to EDX and is used to discover types of atomic bonds. The principle is as follows. A sample is exposed to infrared radiation and the radiation absorbed by the sample is measured according to wave length. Each wave length corresponds to a specific chemical bond which gives the type of material concerned by cross-checking. This technique is particularly used for the analysis of packaging by reverse engineering (in order to determine the materials used and predict their aging behavior) or by seeking to modify their properties in relation to their initial properties (in particular, for polymer packaging materials, excess heat may modify the conformation of molecules).

- Infra-red thermography: with this technique, we use the infrared radiation emitted by a component (in this case the technique is non-destructive) or by the chip of an integrated circuit under normal operating conditions with no additional stress. The aim is to locate hot spots or spots that are hotter than expected. It is then possible to locate a failure quite accurately.

- Acoustic tomography: this can be carried out before opening the casing. This method of

analysis is based on the propagation of sound. Generally, the component or the PCB is

immersed in a shallow depth of water and ultrasound is applied to the surface of the sample.

We then measure the acoustic wave reflected by the different interfaces or that transmitted

through the sample. After appropriate processing of the signal, it is possible to detect

problems of adhesion between two internal layers (in the middle of a multilayer PCB for

example), delamination, etc.

- Emission microscopy (EMMI): this is a non-intrusive optical analysis technique used on the chip of a component in order to detect certain specific faults, such as the consequences of ESD (electrostatic discharges see below), the susceptibility of a circuit to the phenomenon of hot electrons, certain leak currents, latch-up or problems of floating gates. The aim is to view faults using their signature in the visible or near infrared band when the component is in operation. It provides for very accrual physical location of the fault.

- OBIRCH (Optical Beam Induced Resistance CHange): OBIRCH [8] is the most commonly used laser thermal stimulation technique. The laser stimulation will lead to thermal changes inside the chip and reveal the differences in thermal behavior between a sound area and a defective area in the same chip. This difference will mainly be visible on the resistance of the zone heated. OBIRCH is mainly used to reveal problems due to electromigration. There are other similar techniques, such as XIVA (eXternal Induced Voltage Alteration) and TIVA (Thermally Induced Voltage Alteration).

- Pull test and shear test on bondings: after opening the casing, it is possible to carry out mechanical pull and shear tests on the bonding wires on chips to make sure that the wire is secure and test for the presence of excessive thickness of intermetallic compounds (IMC) on the interface between the pad and the bonding. We also can detect other problems, such as brittleness of excessively fine bonding wire.

- Measurement of the integrity of passivation: the aim here is to measure the dielectric properties and homogeneity of the various passivating layers.

There are many techniques that could be used and the list above, which is far from being exhaustive, gives those most often used by EDF R&D. It should be noted that most of these techniques are only used for active components. For passive components, such advanced techniques are only very rarely used, since failure modes are much simpler and a simple micro section, together with SEM examination, if necessary, is enough to find the cause of the failure. Furthermore, the causes of failures of passive components are very limited. Accordingly, they are not checked systematically, allowing greater concentration of efforts on active components.

#### Extrapolation to the Anticipation of Aging

The destructive testing of components is a technique so powerful that it is not limited to the analysis of failures, it also enables us to detect of the signs of aging well before the appearance of a failure. It is possible to perform such tests on components sampled at random in operation to assess their aging. These methods are particularly useful for estimating the aging of solders.

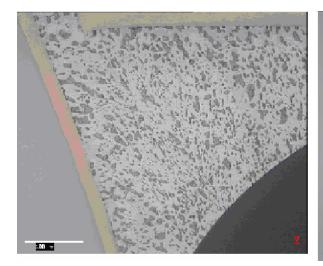

Indeed, for solders made of Sn<sub>63</sub>Pb<sub>37</sub> (the vast majority in French nuclear power plants), observation of the microstructure is the only technique capable of determining the state of aging of the solder. The term microstructure refers to the shape, size and overlapping of the different metallurgical phases in the solder. This is visible on Figure 3-7. The image on the left shows the micro section obtained from a slightly aged solder. We observe a relatively disordered structure. On the other hand, the image on the right shows the micro section of a solder after aging (30 years in operation). We observe that the phases of lead are ordered and that a dendritic growth of this phase has occurred. In general, the longer a dendrite and the more arms it has, the more the solder has aged. In the long term, the phase coalescence will weaken the solder so that it will no longer serve its mechanical purpose. Furthermore, the micro section is used to measure the thickness of the intermetallic compound (IMC) between the PCB and the solder and between the component and the solder. IMC that is too thick will lead to loss of adhesion of the solder on the PCB or component. Furthermore, excessive thickness of an IMC will prevent the component from being repaired back into good condition, should it fail. Moreover, in the literature the change in the thickness of IMC is modeled by various empirical formulae, such as Hwang's formula [9] or Engelmaier's model [10], which have been updated since the publication of the RoHS directive, or their derivatives and less complete versions.

Figure 3-7

Aging of the microstructure of solders (left): solder less than 5 years old: (right): solder after aging for 35 years [11].

Another interesting aspect is that when the role of such solders is known (namely the service life of the board and the temperatures it is exposed to during its life), it is possible to trace the residual life span of the solder on the basis of these empirical models. This enables us to anticipate future failures.

#### Coverage Ratio and Rate of False Failures

Destructive testing is also a good way of determining the coverage ratio of a tester and the rate of false failures or RAS (Nothing to Report). For information, a RAS is a component (or electronic circuit board) deemed to be defective but for which no failure was found during electrical tests carried out once the circuit board was removed from its slot. There may be several possible reasons. First, the board is not actually defective and was sent for repair by mistake. Second, the board may be defective but the tester used during the repair and/or analysis of the failure was not comprehensive enough to confirm the failure (in this case, we talk of inadequate test coverage). If destructive testing reveals a physical cause of the failure, it is obvious that the testing procedure should be revised to improve the coverage of the testing. On the other hand, if no failure signature is found, it is not possible to know whether the component was actually functional before the analysis or if, on the contrary, the failure is real but the analysis was not detailed enough to reveal signs of failure.

It should be noted that this approach may quickly become very time-consuming and costly. Let us take the case of a component reported as defective by the personnel of the power plant but found not to be defective during the electrical test. Generally, the procedure followed at EDF means that for as long as the board has not had its third RAS, it is re-qualified if necessary and put back into service. Following the third RAS, it is scrapped and sent to EDF R&D, which may decide to carry out a destructive test post-mortem. In this case, it is not possible to direct the failure analysis in advance since we have no idea of its cause as the fault has not been confirmed. We must, therefore, resort to very detailed analysis using a large number of analysis techniques (which are not always compatible: for example, when we take a micro section it is very difficult to take several cross sectional planes on the same chip of a component). Such an analysis of an active component typically costs more than 5,000 per component (and may, in certain extreme cases exceed 20,000 per component, particularly when detailed analyses of the chip are concerned), not counting the time required to carry it out. That is why EDF R&D only occasionally conducts destructive tests on the boards scrapped owing to RAS (less than one case in ten). It is preferable to try to assess the coverage ratio of a tester and test RAS boards on other additional test benches to check whether these test benches confirm a failure not detected by the first test bench.

#### Some Examples

As mentioned above, destructive testing is used to reveal internal failures. This section describes a certain number of detectable failures taken from failure analyses carried out by EDF R&D.

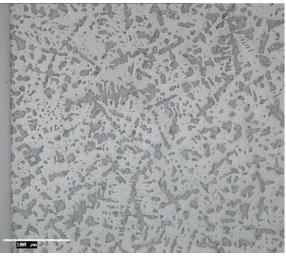

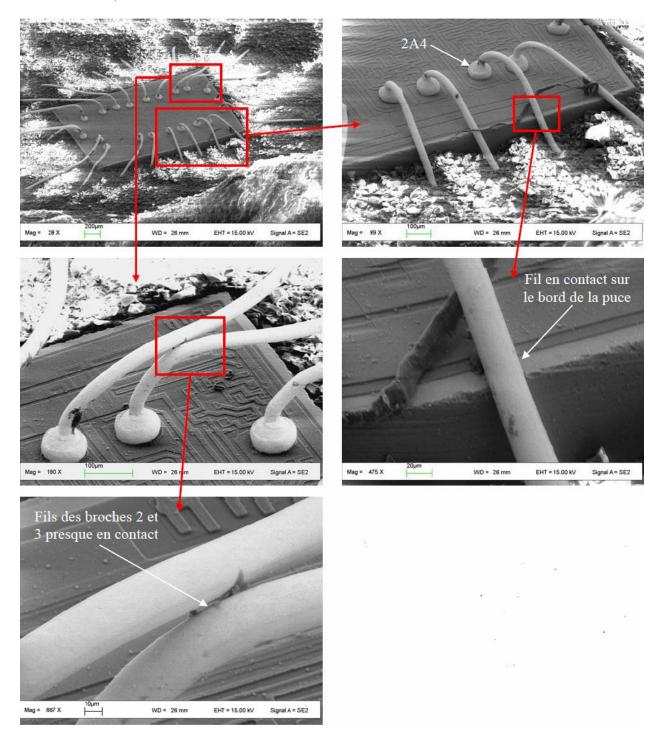

• Wiring fault between the chip and the leads of an SN74LS244 type component in a DIP20 type casing. The images taken with the SEM and shown in Figure 3-8 show a direct contact between the wire of pin 2A4 and the chip, leading to a leak current causing the leak observed in the electrical test on the component. Furthermore, there is a virtual contact between two wires (left hand side of the image); nevertheless, zooming in shows that while this position is not normal, there is no contact.

### Figure 3-8 SEM images of the chip of a Texas Instrument SN74LS244N.

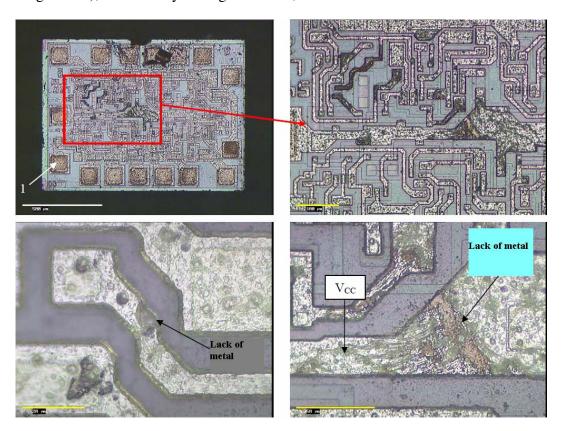

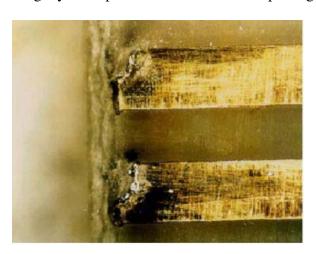

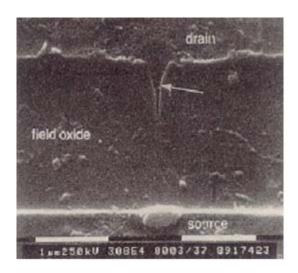

• Electromigration on the chip of a DM74LS279N (RS flip-flop) in a DIP16 casing manufactured by National Instrument. The electrical test revealed a VOL parameter with an abnormal value on one of the four outputs of the flip-flop. A lack of metal on the suspect circuit due to a phenomenon of electromigration, shown after opening on the SEM image (see Figure 3-9), followed by damage to tracks, caused the failure observed.

Figure 3-9

Lack of metal, effects of electromigration on the chip of a RS flip-flop.

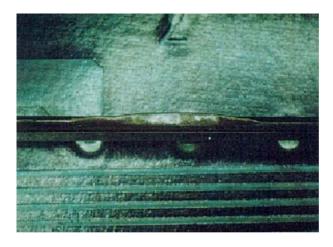

• Migration of aluminum (electromigration) on a track connected to the VSS input of a Mostek MK4118P-2 (SRAM memory), leading to cracking of the passivation and extrusion of aluminum on the surface of the chip and failure (see Figure 3-10).

Figure 3-10

Presence of cracking and extrusion of aluminum on the chip of a SRAM memory.

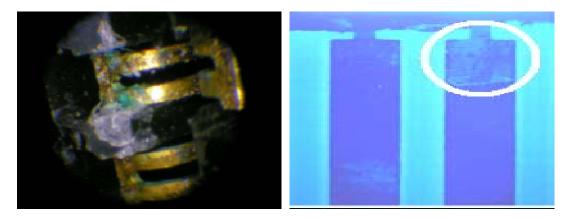

Oxidation and presence of impurities on a BZX85C diode owing to loss of sealing of the casing. A defective BZX85C diode was immersed in a bath of a fluorescent liquid under pressure. Figure 3-11 clearly shows in ultraviolet light, that the liquid has penetrated the diode as far as the chip. A micro section of the chip then confirmed the presence of impurities and oxidation, explaining the failure observed.

Figure 3-11 (left) BZX85C diode in white light (right) and in ultraviolet light after being placed in a fluorescent liquid under pressure.

• Presence of resistive filaments in the chip of a 2N2222 transistor probably due to a partial electrostatic discharge (see Figure 3-12). These filaments were observed by emission microscopy (EMMI).

Figure 3-12 EMMI image of the chip of an almost defective 2N2222 transistor.

#### Actions to be Taken After a Failure Analysis

Once the failure analysis has been carried out, it is important to document it in a data base including as much information as possible. Ideally, it should include the following data at least:

- Type of component.

- Date-code.

- Manufacturing plant.

- Cause of failure.

- Site concerned.

Generally, the first three items are mentioned, with varying degrees of clarity, on the packaging of the component analyzed. EDF R&D has over the years collated a data base with some 2000 failures (for the entire stock of electronic components with EDF, not only from nuclear power plants). Therefore, it is now possible to take the failure analysis approach to the limit by making correlations between the various parameters. Now it is relatively easy to detect:

- Generic failures (same type of component, observed on several sites and for components from various manufacturers).

- Problems in manufacturing (series of poor quality, etc.), these failures concern a specific date-code or given plant.

- Cause specific to the environment or maintenance policy of a site (if failures of the same type are observed on a single site).

Nuclear facilities are now capable of taking appropriate measures (preventive replacement of the components installed, modification of MRO practices, etc.).

#### Recommendations for the Use of Failure Analysis

On the basis of the previous discussion, it is clear that EDF R&D is relying heavily on the destructive testing of components, which forms part of the following approach:

- Systematic destructive testing of defective active components in order to determine the cause

of the failure and, of considerable importance, whether this failure is generic or not. For

information, in 2010 EDF R&D has analyzed more than 300 active components considered

to be defective by systematic analysis.

- Research into aging of components, the properties that drift but are still within their specifications. In this case, the analysis is not systematic. It is only carried out when the drift observed concerns sensitive equipment or when it appears to be generic. Such an approach was used; for example, for 2N2222 transistors [12-13].

- Regular monitoring of the aging of solders. Given the slow rate of change to the

microstructure of solders, it is not necessary to carry out these analyses annually. Overall

monitoring of representative boards, carried out once every five years for example, is more

than enough. For information, EDF R&D carried out analyses of this type in 2009 and has

not scheduled to do them again, given the good state of aging observed.

- Determination of the rate of NTD (Nothing To Declare) and the coverage of the testers used.

- Setting up a data base of the failures or aging components observed.

#### **Monitoring Reports from PCB Repairers**

As shown in the previous sections, failure analysis is a powerful tool for anticipating failures. Nevertheless, it requires an enormous amount of time and it is not always easy to do systematic analyses of the components found to be defective. Another useful indicator is provided by the PCB repairers themselves, who count the number of components actually replaced every year. This provides very reliable trends for the aging of instrumentation and control systems and it also detects significant increases in the number of failures for a given function or type of board.

Ideally, the repairers' statistics on the causes of failure should be compared with those from EDF R&D. At present, this comparison is planned but has not yet been made.

#### **Summary**

In addition to purely visual inspections, various additional methods for assessing the aging of printed circuit boards have been described here. On one hand, specific testers may be developed in order to analyze the main aging mechanisms suspected. This is true for passive components (capacitors in particular), optoelectronic couplers, thyristors and, more generally, power components.

48BAdditional Inspection Approaches for Printed Circuit Boards

The best method for determining the state of aging or finding the cause of a failure is still destructive testing. It should be carried out systematically on all defective components but also on an individual basis on aging components to assess their precise state of aging and predict their residual life span. Given the destructive nature of these analyses, it is obvious that the number of components just aging tested this way should be limited.

To stipulate the types and volume of components to be analyzed, we should also study PCB repairers' reports, in addition to results from destructive testing.

Therefore, by combining visual inspection techniques with the good practices described in this chapter, it is possible to obtain a reliable view of the state of aging of installations, not taking system level into consideration but electronic components themselves.

## 4

# TECHNOLOGY WATCH OF OPERATING EXPERIENCE IN OTHER INDUSTRIES